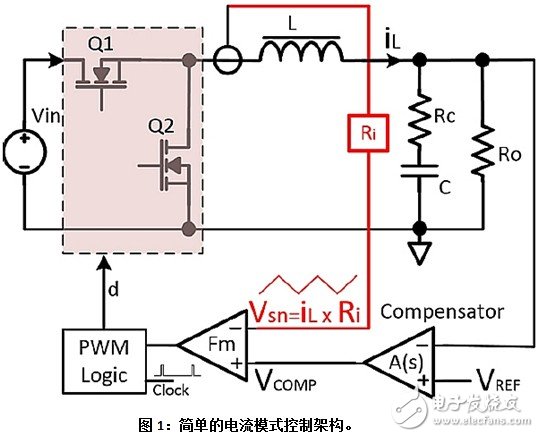

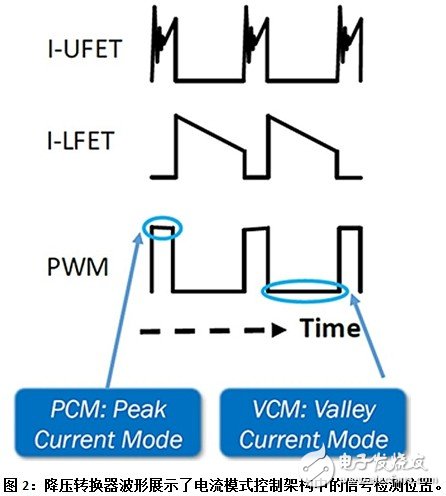

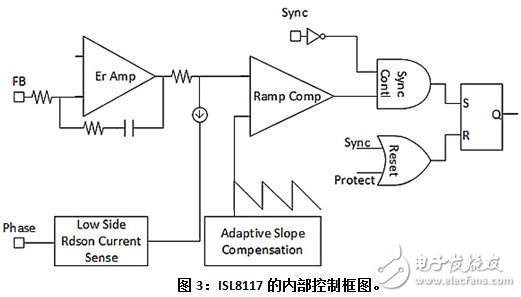

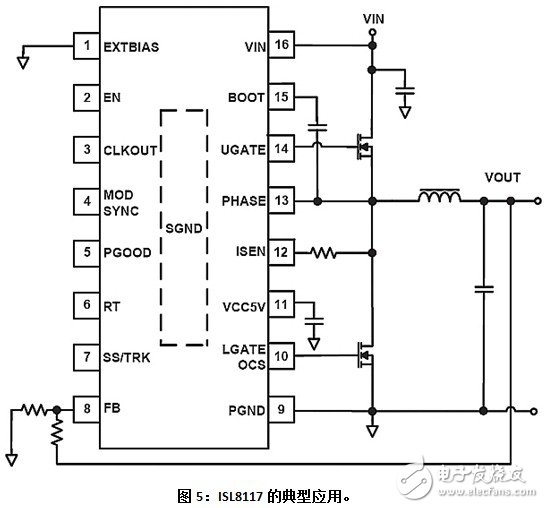

With leading-edge DSPs, FPGAs, and CPUs operating at lower and lower supply voltages and consuming more current, choosing a PWM controller is not that easy. Voltages below 1V become very common, while the intermediate bus voltage remains essentially constant and even increases in some specific applications. System frequency is also steadily increasing to support smaller inductor and capacitor (L&C;) filtering. Last year's 500kHz has become 1MHz this year. In high-voltage applications that require lower output voltages, power supply designers typically rely on modules that increase system cost, or two-level DC/DC solutions that increase solution form factor and complexity. This article focuses on trends affecting narrow on-time point-of-load (POL) conversion and compares it to commonly used current mode control architectures. The article discusses a hybrid valley current mode (VCM) architecture with adaptive slope compensation, including the use of a new 60V synchronous buck controller that combines conditions in a wide range of Vin and Vout conditions. Stable operation at low duty cycles allows direct step-down conversion from 48V to 1V point of load. Demand for narrow on-time load point conversion Buck converters are the most widely used power supply topology, and recent trends indicate that next-generation switching controllers must be able to provide stable and efficient operation at very low duty cycles. While current mode control methods have many advantages over voltage mode control, there are some limitations inherent in application requirements, particularly in terms of duty cycle limitations. In general, power supply systems in both telecommunications and industrial applications use multi-stage conversion circuits. There is also a continuous power supply system where the load point input voltage changes from 3.3V to 5V to 12V over time. As power requirements increase, the use of 12V rails is now common, and the use of 3.3V rails is becoming less common. This trend toward higher input voltages is partly due to the fact that larger currents cause I2R (current to resistance) power losses and related problems that occur in low voltage circuits. Recently, this trend is still moving toward higher voltages, such as 24V to 42V for industrial applications and 48V for telecommunications. Continued technological advances have made it possible to control narrow pulses. At the same time, new research shows that higher input voltages can achieve higher overall efficiency, lower system cost, and increase system reliability by reducing the temperature of the distribution path. Another factor driving the PWM narrow pulse requirement is the need for higher switching frequencies, which will result in higher power densities. It is common for power supplies to operate at 1MHz switching frequency. In fact, in automotive infotainment applications, this switching frequency needs to exceed 1.8 MHz in order to avoid the amplitude modulation band. A 12V to 1V power conversion at 1MHz still requires 83ns of pulses. Limitations of low duty cycle operation An ideal buck converter can generate any voltage below Vin, even to 0V, but there are many limitations in practical applications, such as reference voltage, internal or external circuit losses, and more importantly, the modulator used to generate the control signal. Types of. For a particular input voltage, the reference voltage is the most obvious limiting factor that prevents the controller from covering the entire range from 0% to 100%. The most obvious is the reference voltage: This formula shows that the output can be adjusted below the Vref voltage. The second major limiting factor in achieving the minimum Vout is the minimum on-time of the controller. For a given input voltage (Vin), the minimum Vout can be expressed as: For a given switching frequency (Fs), the on-time of the upper MOSFET is equal to: The control method used by the controller is mostly used to drive the minimum on-time that it can control. Some intentional delays inside the gate drive circuit, such as blanking time, also affect the minimum on-time. In a typical current mode PWM controller, the magnitude of the PWM pulse depends on the output of the error amplifier and the inductor current signal, as shown in Figure 1. The current loop detects the inductor current signal and compares it to the VCOMP reference value, which is used to modulate the PWM pulse width. Since the current loop forces the peak or valley current of the inductor to follow the voltage error amplifier output, the inductor does not appear in the voltage control loop. For voltage loops, the two-pole LC filter will become a single-capacitor pole structure. A simple type 2 compensation is sufficient to stabilize the voltage loop. Modulator suitable for narrow on-time operation Peak current mode control is one of the most commonly used architectures, and while it is well understood, it can provide reliable control techniques with many advantages, but presents significant shortcomings when working with narrow on-time requirements. In peak current mode, the inductor current information is detected on the upper MOSFET. Figure 2 shows a typical current waveform associated with a PWM signal in the upper and lower MOSFETs. The turn-on event of the upper MOSFET can cause significant ringing due to different parasitic parameters inside and outside the MOSFET in the turn-on loop. This ringing sends an error signal to the control circuit and erroneously terminates the PWM signal. To solve this problem, the peak current mode switching controller ignores this initial ringing using the blanking time before detecting the inductor current. The blanking time normally set is 150ns to 250ns. This blanking time requirement does not allow the peak current mode controller to regulate power conversion for very narrow on-times. At 600kHz, even a 12V to 1V power conversion is difficult to adjust. This frequency is equivalent to a minimum on-time of less than 140ns. Valley current mode control Another method is valley current mode control, which easily overcomes blanking time defects under peak current mode control. Under the control of the valley current mode, the detection of the inductor current signal is performed during the off period of the upper MOSFET, thereby avoiding the ringing of the upper MOSFET. This method solves the problem of controlling very narrow on-time PWM pulses. However, the valley current mode has its own limitations. There are two main problems with valley current mode control, namely subharmonic oscillations and poor linearity adjustment. Subharmonic oscillations are a common problem in any current mode control scheme. It also occurs in peak current mode control, but all occur when the duty cycle exceeds 50%. The opposite is true for the valley current mode. Subharmonic oscillations in current mode controllers (whether peak mode or valley mode) can be avoided with slope compensation. However, fixed slope compensation cannot handle all duty cycles and inductances. Subharmonic oscillation problems can also occur if the duty cycle is far from the setpoint used in the slope compensation design. Peak current mode control Another method is the simulated peak current mode control, which is a variant of the peak current mode that avoids the blanking time limit. This method overcomes the ringing of the upper MOSFET by measuring the valley current information on the low side MOSFET. This valley current information can then be used to simulate the inductor overshoot to obtain peak current information. As in peak current mode control, the simulated peak current mode also has subharmonic oscillation problems that require slope compensation. This slope compensation is derived from the simulated peak current signal. Although the simulated peak current mode design combines the benefits of the bee current mode and the valley current mode control method, it also has disadvantages, mainly due to the lack of inductance information in the control loop. Combines the advantages of both modes The valley current mode with adaptive slope compensation is one way to overcome the shortcomings of conventional valley current mode control. The optimized adaptive slope compensation circuit prevents subharmonic oscillations from occurring under all duty cycle conditions. This inherent ability of adaptive compensation and low duty cycle operation allows controllers with this architecture to operate at very high switching frequencies. Intersil's ISL8117 step-down controller uses a valley current mode control with low side MOSFSET Rdson, valley current sensing and adaptive slope compensation. As shown in Figure 3, the ISL8117's ramp signal can accommodate the applied input voltage, effectively improving line regulation. Its unique valley current mode implementation and optimized slope compensation overcome the shortcomings of traditional valley current mode controllers. The unique control technology of the ISL8117 allows it to support a wide range of input and output voltages. In fact, the ISL8117 is a hybrid of voltage mode control and current mode control, with the advantages of both modulation architectures. The ISL8117 can operate from any voltage in the 4.5V to 60V range and its output can be adjusted from 0.6V to 54V. It has an adjustable frequency range of 100kHz to 2000kHz and can produce a minimum on-time of 40ns (typical). At 40ns minimum on-time, the controller can generate a 1V output from a 12V bus at 1.5MHz. It also produces a 1V supply from a 48V supply at a lower frequency. Figure 4 shows the instantaneous transition from a stable 48V to 1.2V. In systems that are susceptible to noise from specific switching frequencies, the ISL8117 can be synchronized to any external frequency source to reduce radiated system noise and beat frequency noise. With this synchronous buck controller, engineers can design a complete DC/DC conversion solution with only 10 components including MOSFETs and passive components, and achieve 98% conversion efficiency and 1.5% Output voltage accuracy. As shown in Figure 5, the ISL8117's low pin count and layout-friendly pin architecture minimizes the number of cross traces and further improves power supply performance. Summary of this article Each modulation control mode has its own limitations, but recent innovations such as the ISL8117 60V step-down controller with mixed valley current mode and adaptive slope compensation allow for more flexible and convenient design of the power supply. solution. The ISL8117 helps system designers remove intermediate conversion stage circuits to achieve higher power in a smaller footprint while reducing system cost and increasing product reliability. Basic Features Din Rail Terminal Block,Din Rail Fuse Terminal Block,Din Rail Busbar Terminal Block,Din Rail Power Terminal Blocks Sichuan Xinlian electronic science and technology Company , https://www.sztmlchs.com![]()

![]()

1. The terminal has universal mounting feet so that it can be installed on U-rail NC 35 and G-rail NC32.

2. The closed screw guide hole ensures ideal screwdriver operation.

3. Equipped with uniform accessories for terminals of multiple cross-section grades, such as end plates, grouping partitions, etc.

4. Potential distribution can be achieved by inserting a fixed bridge in the center of the terminal or an edge-plug bridge inserted into the wire cavity.

5. The grounding terminal and the N-line slider breaking terminal with the same shape as the common terminal.

6. Using the identification system ZT, unified terminal identification can be realized.

7. The rich graphics enhance the three-dimensional sense of the wiring system.